# Integrated Hardware Architecture and Device Placement Search

Irene Wang<sup>1</sup>, Jakub Tarnawaski<sup>2</sup>, Amar Phanishayee<sup>2</sup>, Divya Mahajan<sup>1</sup>

<sup>1</sup> Georgia Institute of Technology, <sup>2</sup> Microsoft Research

### Training DNN models require **2 simultaneous design choices** to be made to balance resource utilization and memory footprint

#### **1. Hardware Architecture**

#### **2. Device Placement Strategy**

# **Design Choice 1: Hardware Architecture**

#### Explores the on-chip and offchip resource utilization

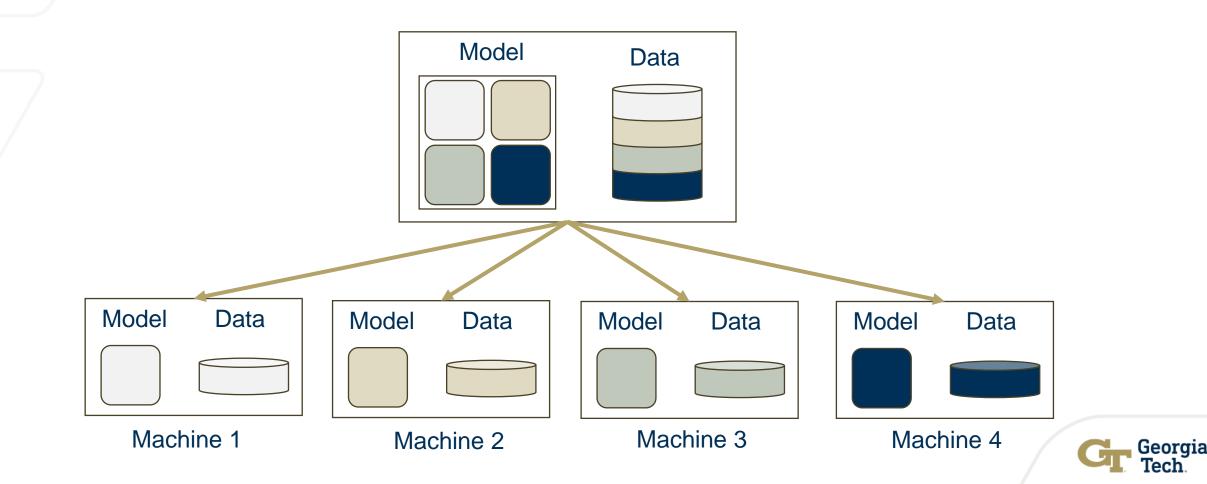

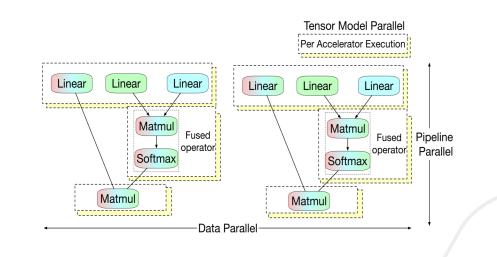

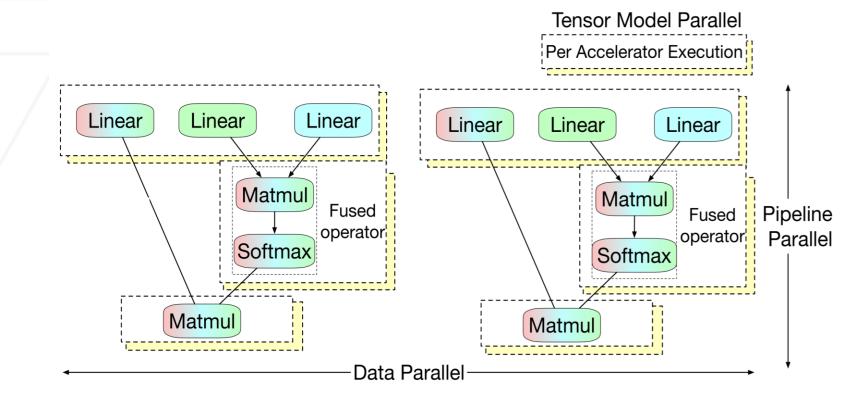

# **Design Choice 2: Device placement**

Balance between:

- Memory footprint

- Networking overhead

- Overall training throughput

# Motivation

What architecture and model distribution strategy can achieve the optimal performance for end-to-end deep learning training?

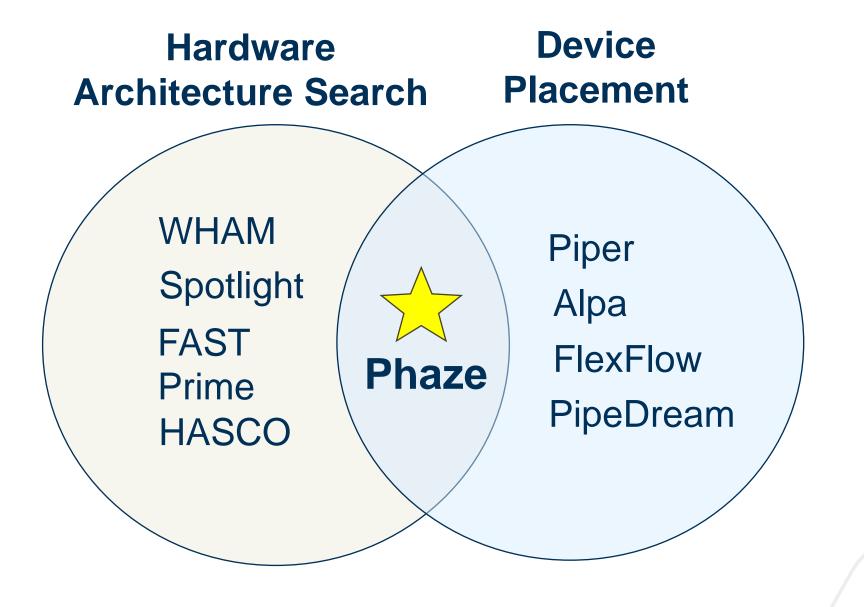

#### **Prior Works**

# **Need for Co-optimization**

**Normalized Area**

# Fixed device placement in architecture search may lead to

hardware under-utilization

**Fixed hardware architecture** in device placement search limit the search space of memory footprint and networking overhead

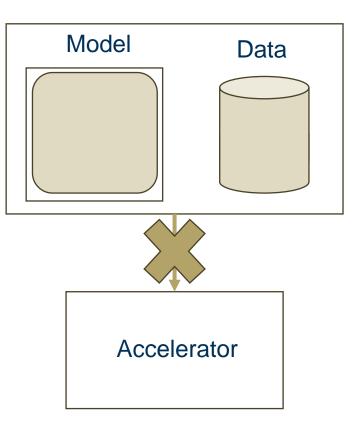

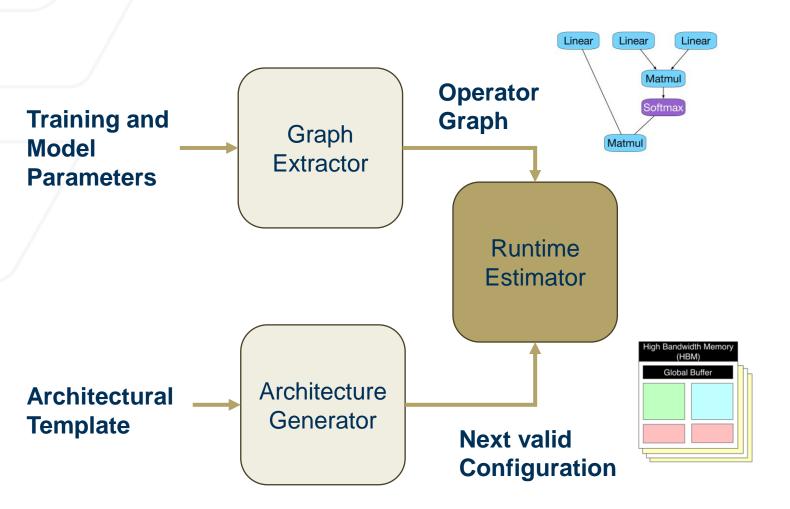

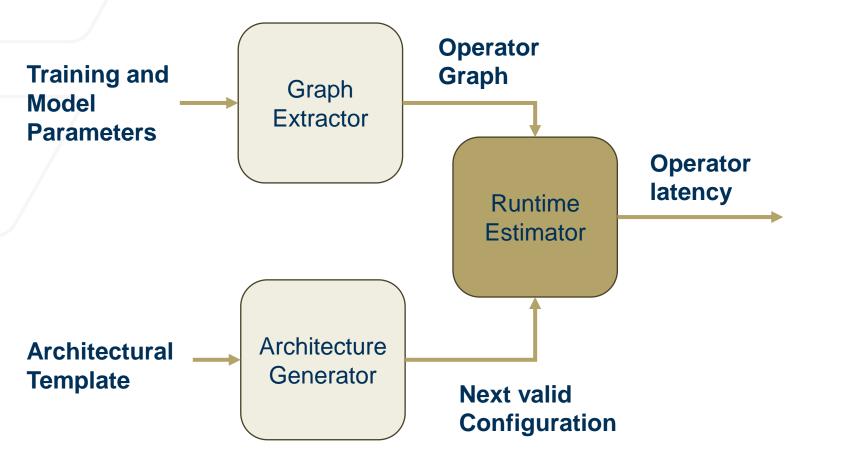

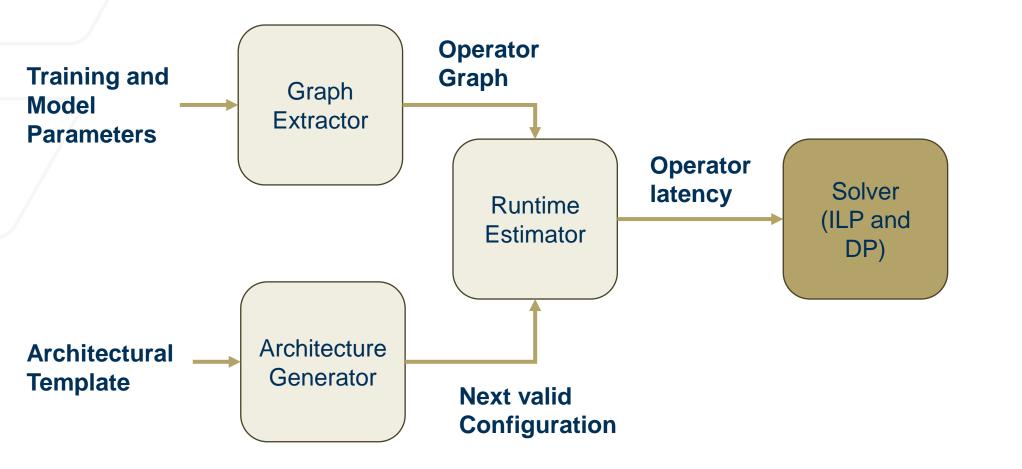

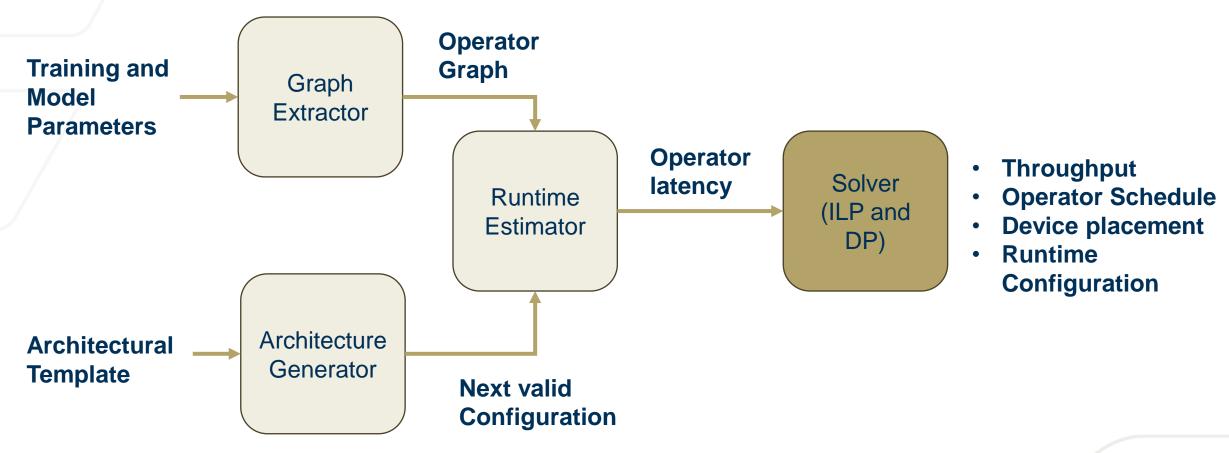

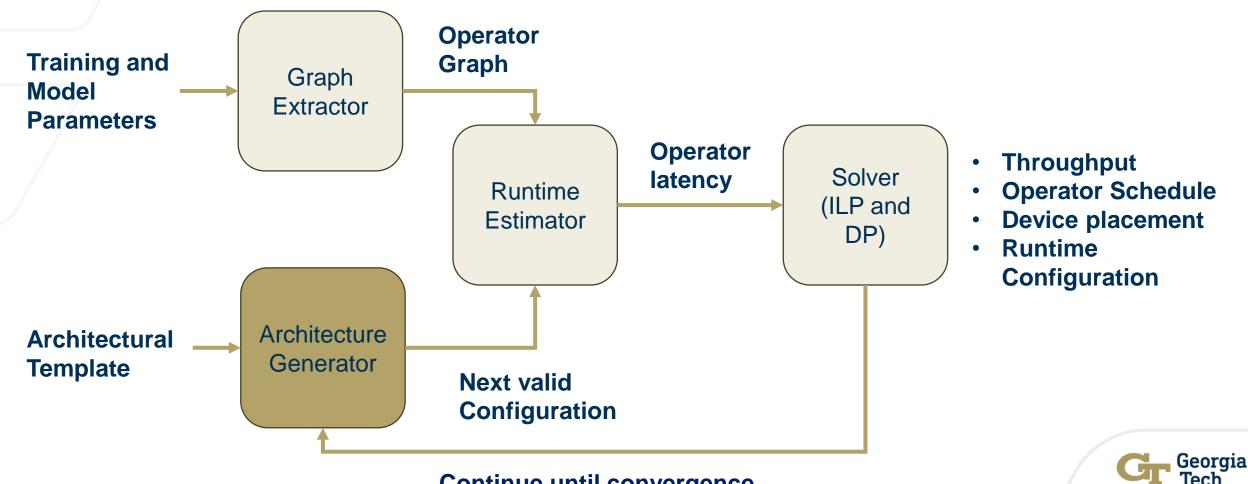

#### Framework for co-optimizing hardware architecture, device placement strategy and per-chip operator scheduling

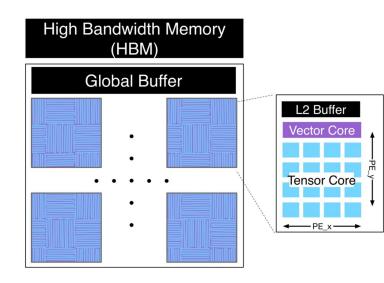

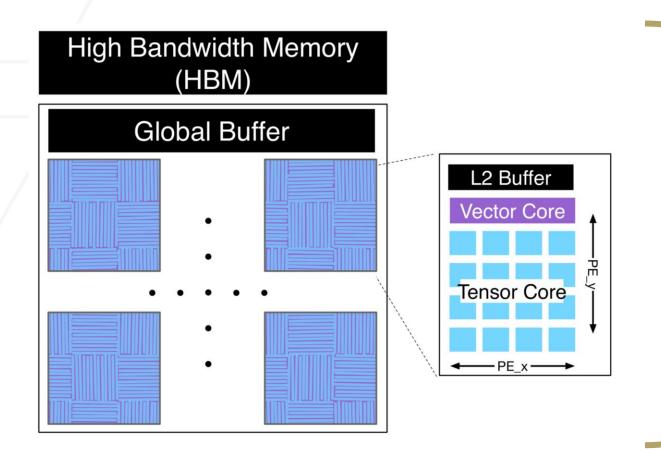

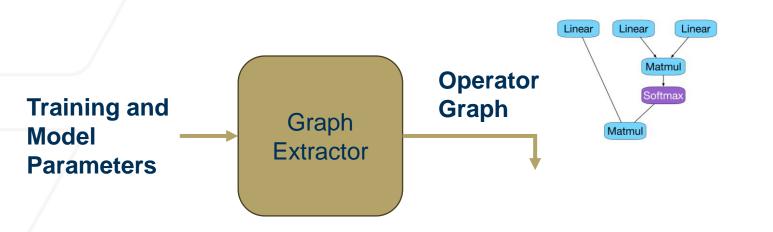

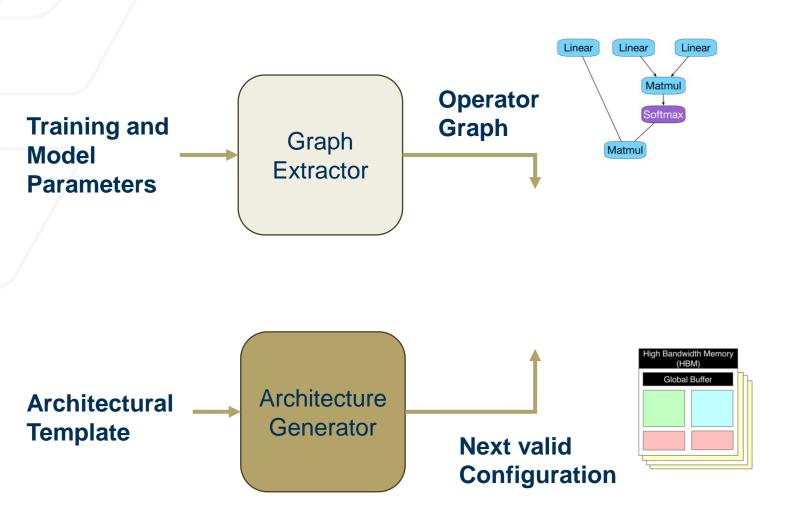

Training and Model Parameters

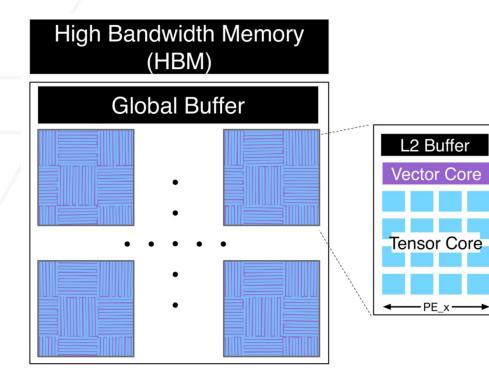

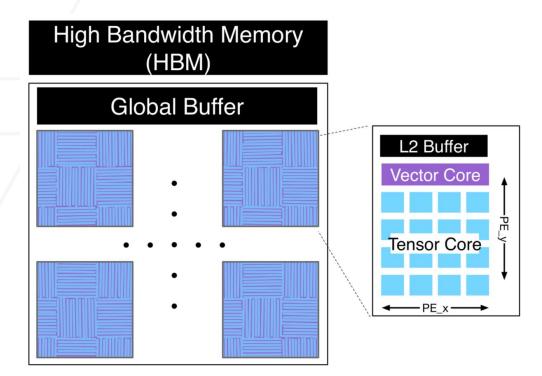

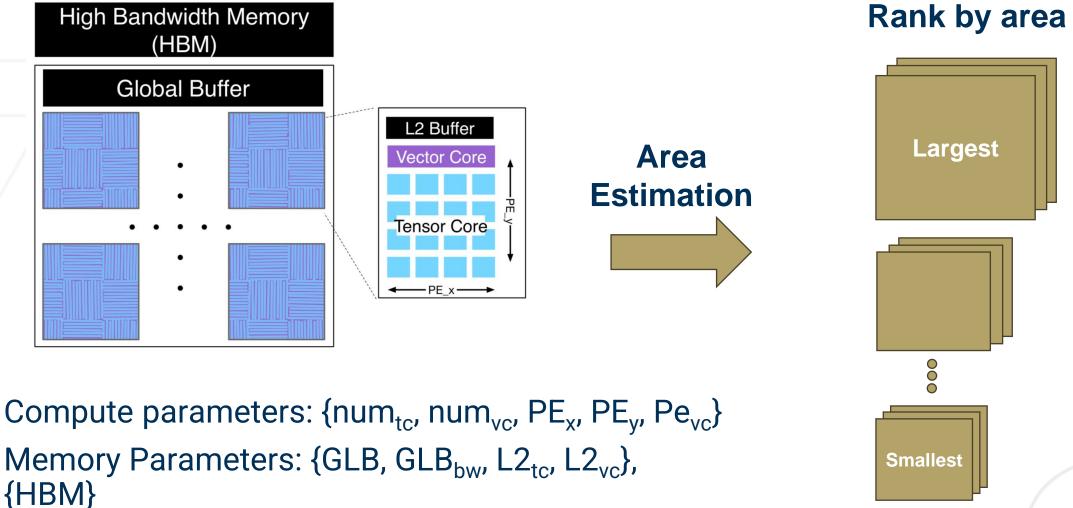

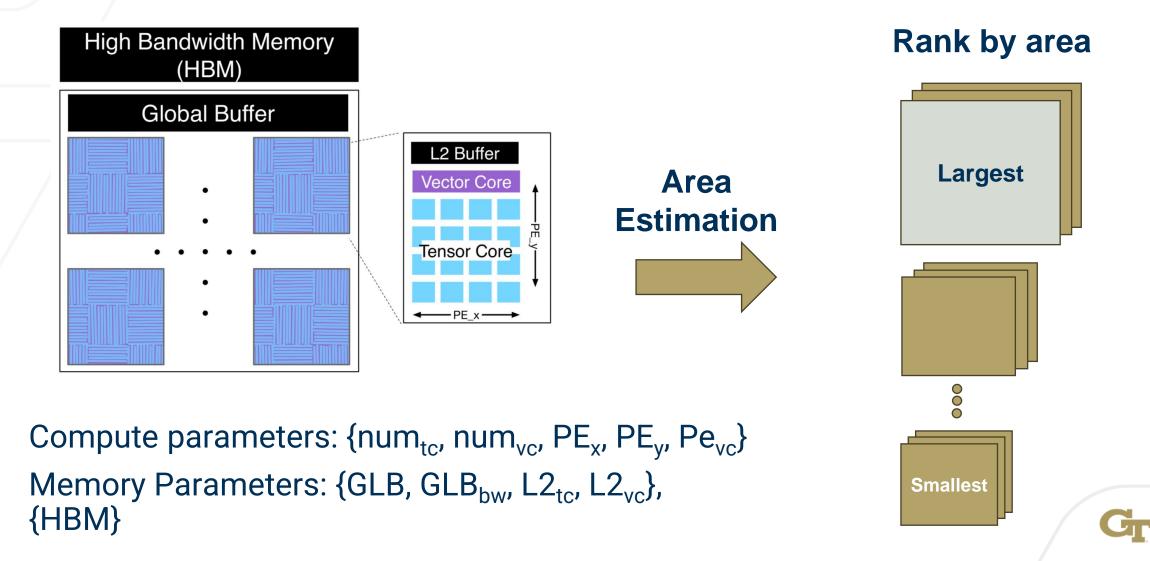

Compute parameters: {num<sub>tc</sub>, num<sub>vc</sub>, PE<sub>x</sub>, PE<sub>y</sub>, Pe<sub>vc</sub>} Memory Parameters: {GLB, GLB<sub>bw</sub>, L2<sub>tc</sub>, L2<sub>vc</sub>}, {HBM}

Compute parameters: {num<sub>tc</sub>, num<sub>vc</sub>, PE<sub>x</sub>, PE<sub>y</sub>, Pe<sub>vc</sub>} Memory Parameters: {GLB, GLB<sub>bw</sub>, L2<sub>tc</sub>, L2<sub>vc</sub>}, {HBM}

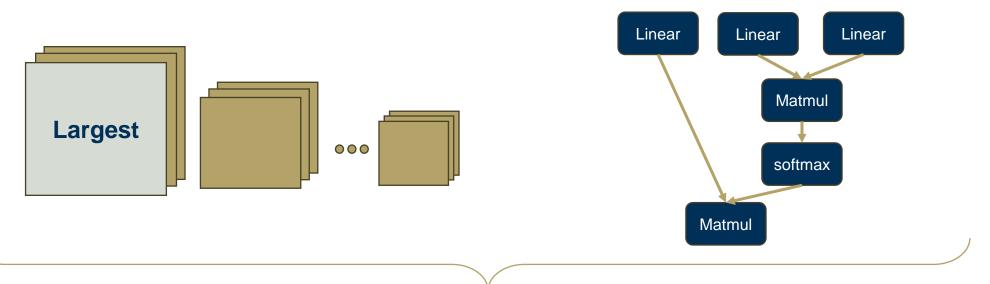

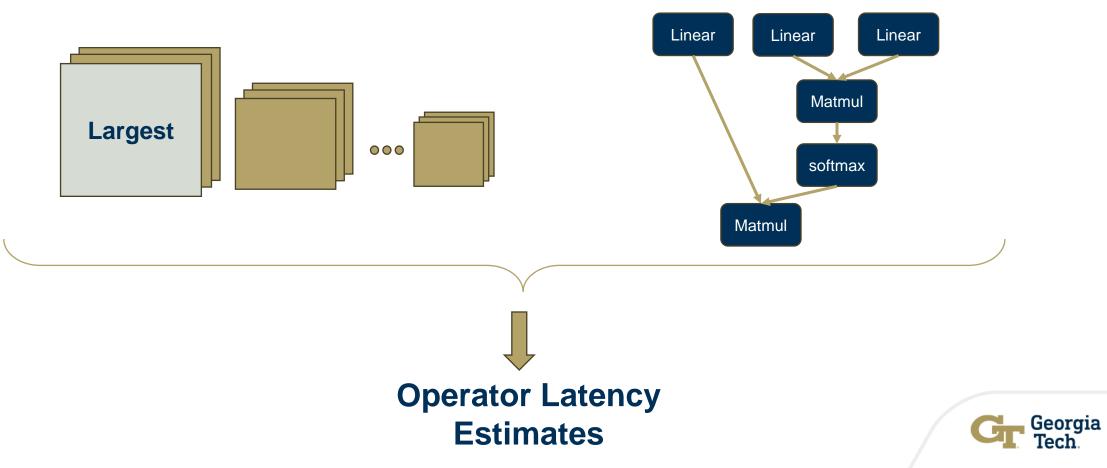

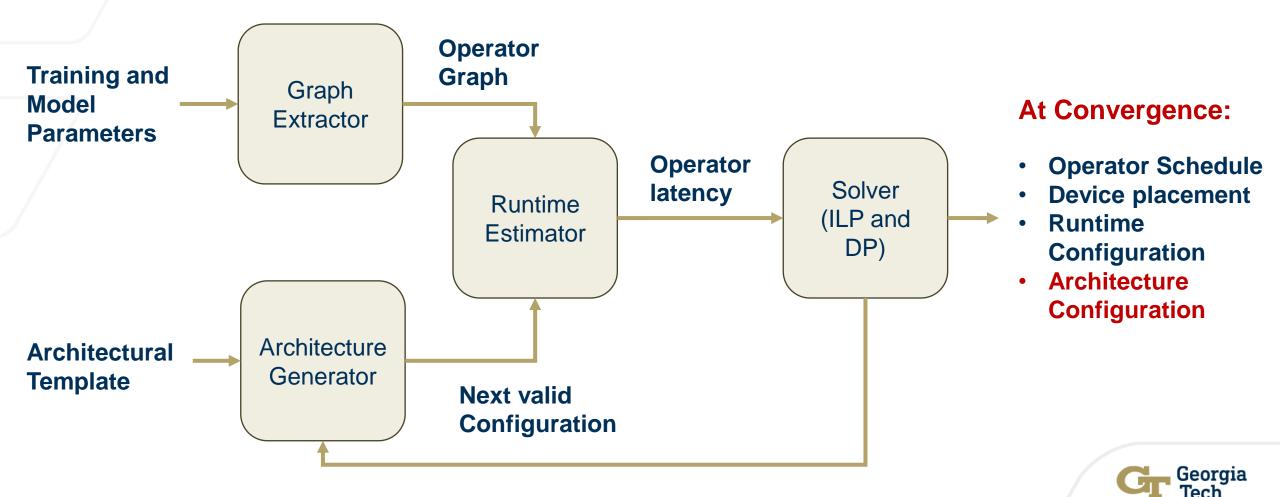

### **Overview of Phaze: Estimator**

#### Next Architecture Configuration

#### **Operator Graph**

### **Overview of Phaze: Estimator**

#### Next Architecture Configuration

#### **Operator Graph**

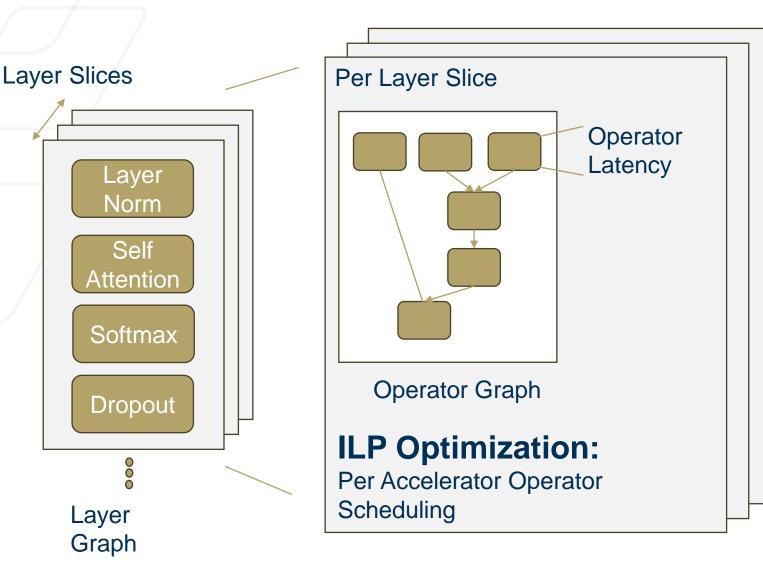

# **Overview of Phaze: Integer Linear Program**

- Constraints ensure:

- Order and dependencies in graph

- Resource constraints are met

- Reduced Complexity without time-indexed variables

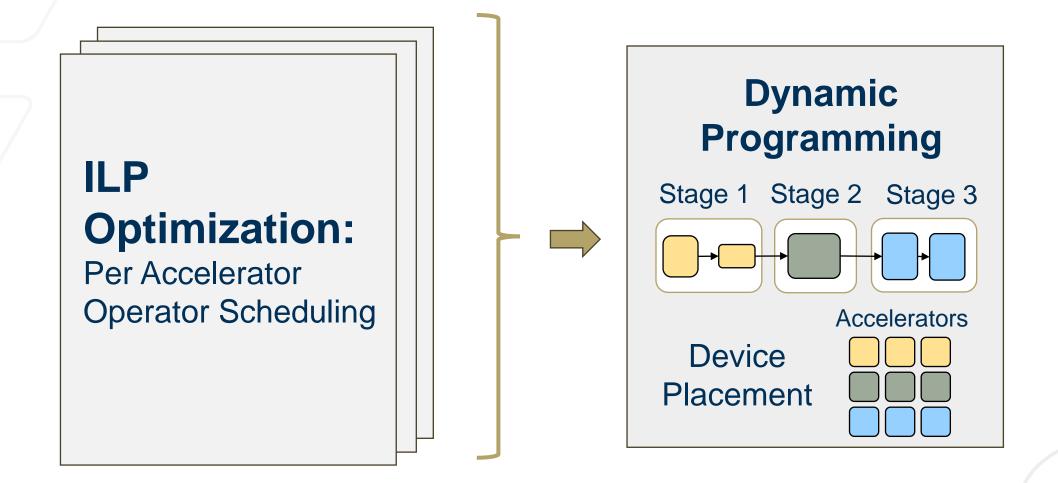

### **Overview of Phaze: Dynamic Progamming**

Continue until convergence

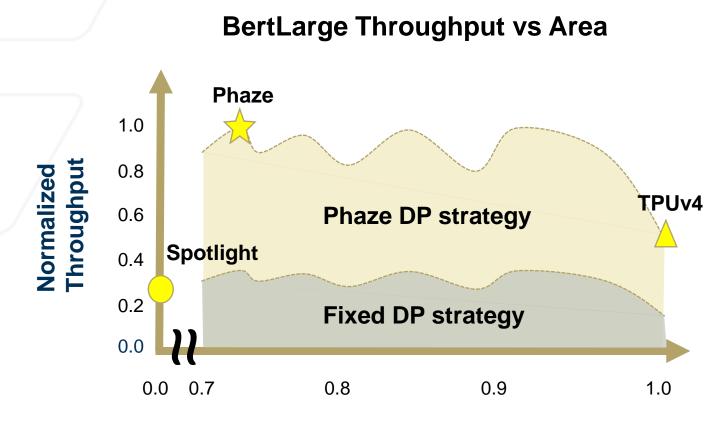

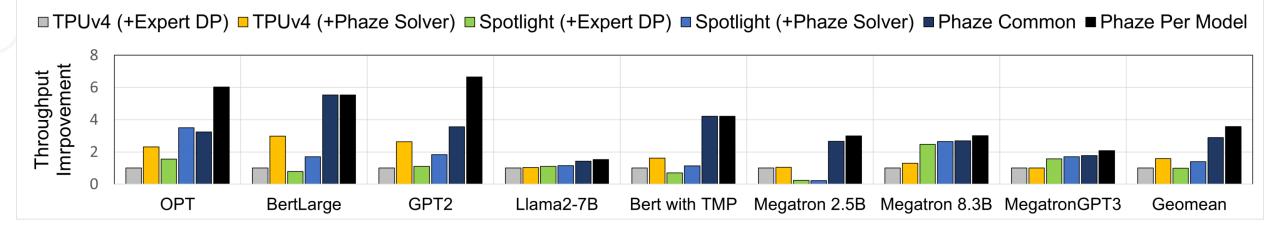

# **Evaluations**

### **Comparison baselines**

#### **Architecture Baselines:**

- TPUv4 architecture

- Spotlight- searched architectures

#### Each architecture is executed with:

- Fixed Expert device placement strategy

- Phaze solver device placement strategy

#### **Throughput Results**

#### Phaze Model specific and Common configurations on average provide 3.6x and 2.9x higher throughput than TPUv4 architecture

### **Phaze Architecture Characteristics**

# 91% area utilization

# Large Tensor Cores

#### High number of Vector Cores

# Conclusion

#### Phaze is an algorithmic solution for distributed training:

# Co-optimization between architecture search and device placement

Novel ILP programs that reduces convergence time

Makes the multi-dimensional search space tractable

Achieves higher throughput compared to state-ofthe-art solutions

# **Future Work**

### Adding New Evaluation Metrics to Phaze

- Carbon

- Power

- Cost

- Adding Support to model more realistic networks

- Current Assumes a flat network

- More sophisticated collective communication modelling